### The FlashCam Project A fully digital camera for future Cherenkov telescopes

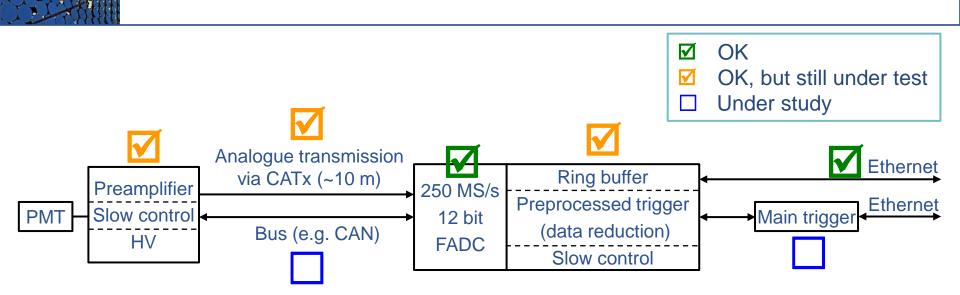

- FADC-based system

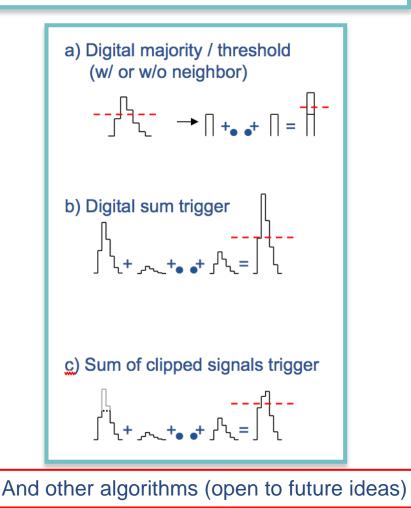

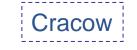

- Digital FADC/FPGA trigger

- GBit Ethernet front-end readout

Speaker: Arno Gadola, Uni. Zurich

### FlashCam: Extensive Simulations ...

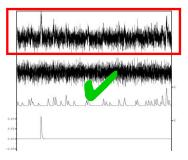

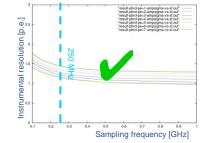

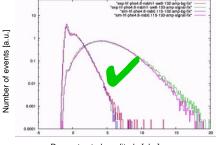

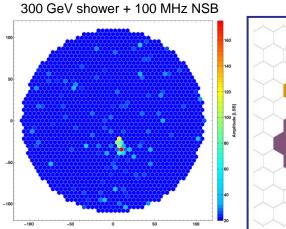

Simulations and measurements have shown: 250 MS/s digitization highly competitive **MC WP is starting to implement 250 MS/s digitization for cross-check**

# Simulation of 2GS/s and 250 MS/s digitization

Resolution above 250 MS/s approx. constant (simulation)

Comparison and confirmation of resolution at 2GS/s and 250 MS/s with measurements

MPIK + Uni Zurich

Trigger topology-, time jitter-, NSBand other studies

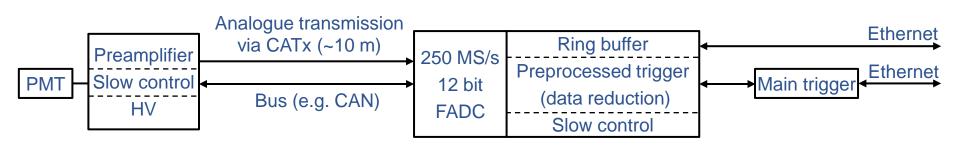

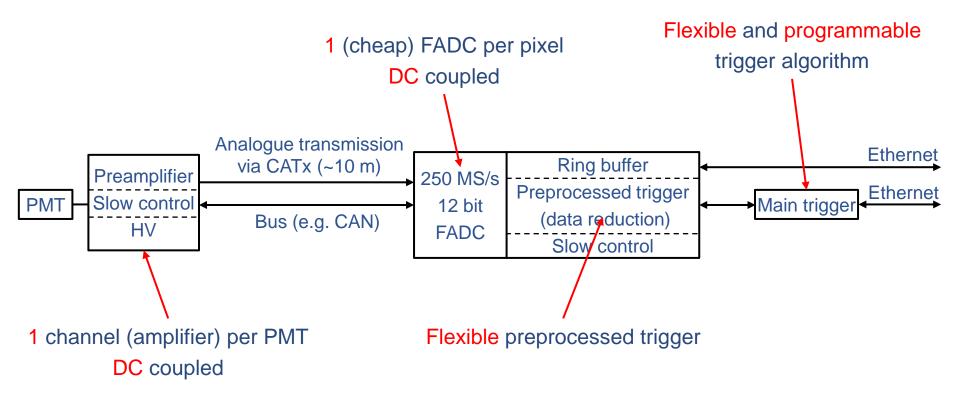

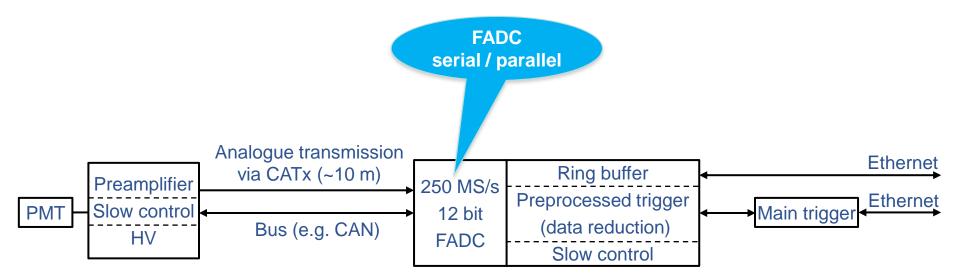

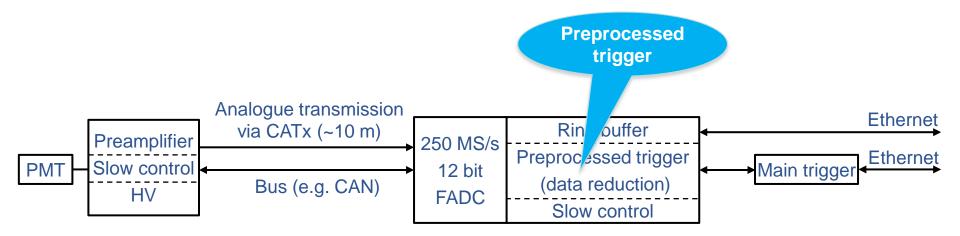

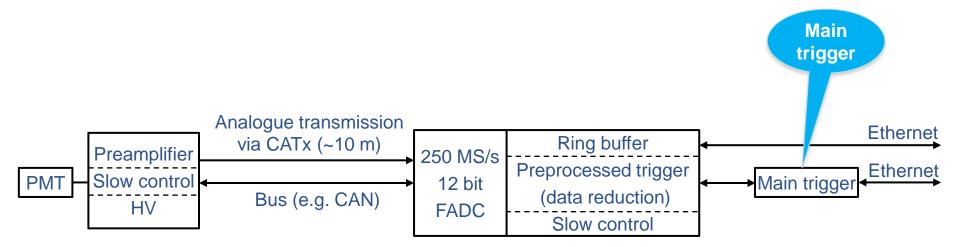

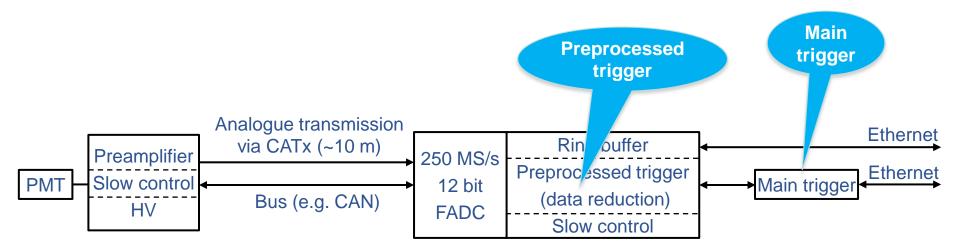

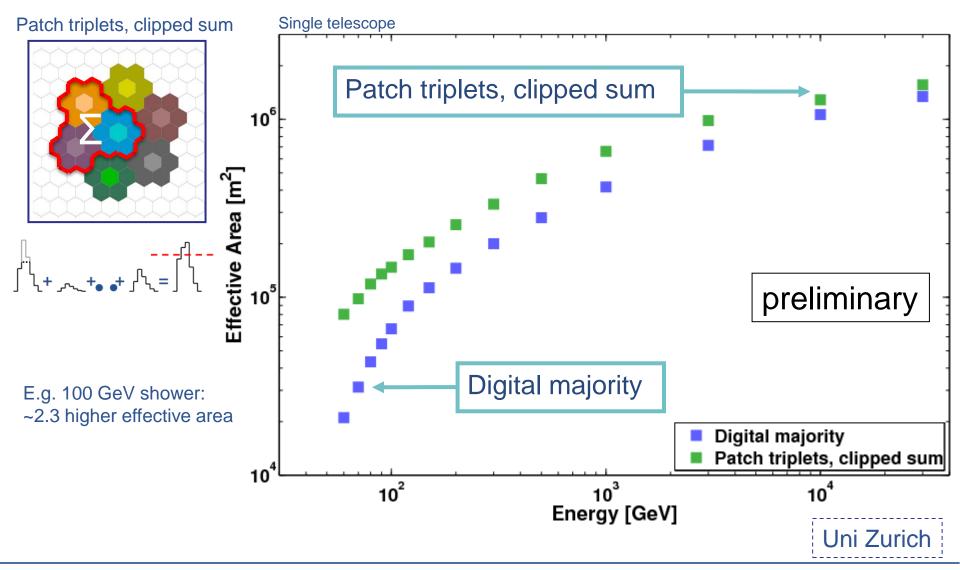

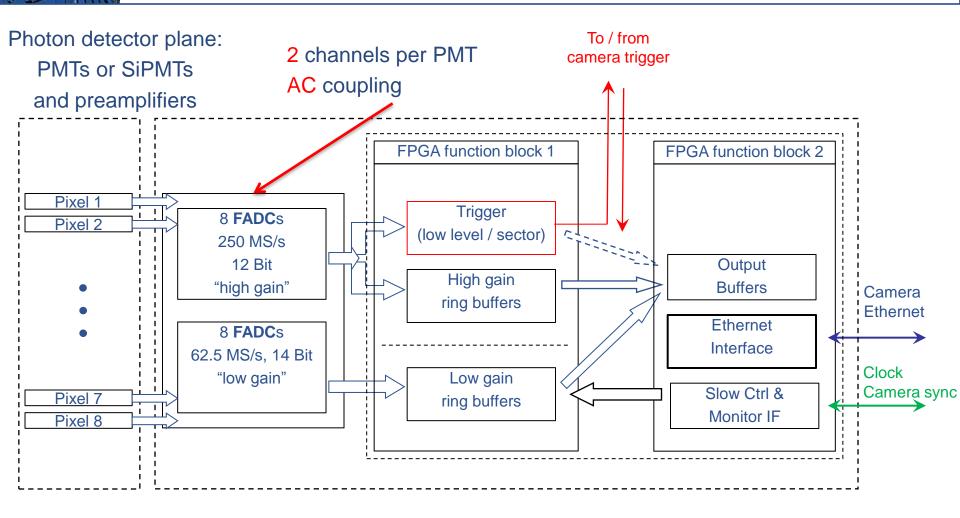

### FADC-based front-end: Baseline topology

## FADC-based front-end: Features

Slow control

### Preamplifier

### **Nonlinear preamplifier**

Only one amplifier per PMT needed

only one (12-bit) FADC per PMT

- Three approaches:

- op-amp in saturation

- transistor in saturation

- nonlinearity of diode

Cracow + Uni Zurich + MPIK

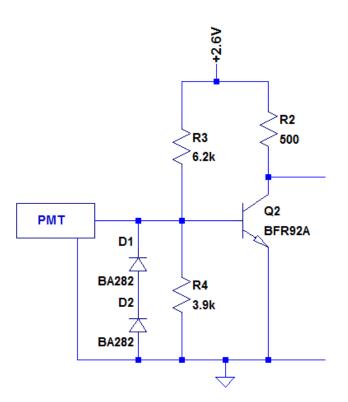

### Saturation preamplifier: baseline

- ~0.1 to 3000 PE dynamic range

- Saturation starts at about 200 PE (~ 8 LSB / PE)

- Saturation is a documented feature

- Working on variable gain

- Baseline solution for parallel FADC demo board

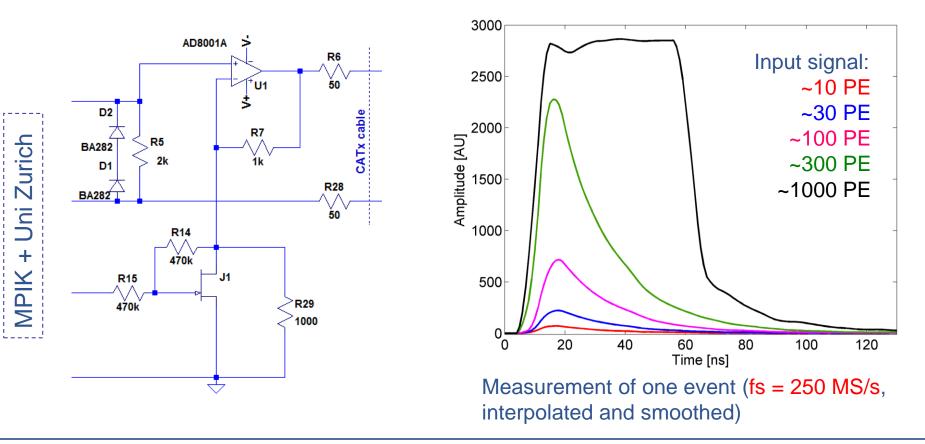

### Transistor preamplifier: option I

MPIK + Uni Zurich

- ~0.1 to 3000 PE dynamic range

- Saturation starts at about 200 PE (adjustable through power supply voltage)

- First measurements done

• Cheap and low power (~15 mW/pixel)

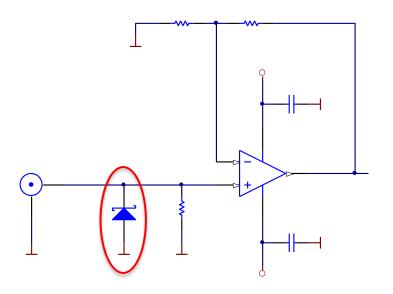

## "Diode" preamplifier: option II

- Nonlinear preamp simulated and tested in the lab

- More development needed

N - 1

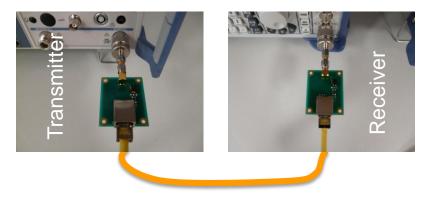

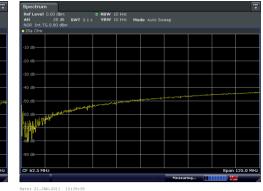

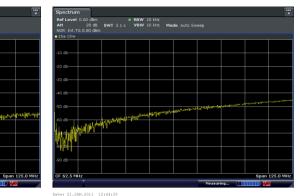

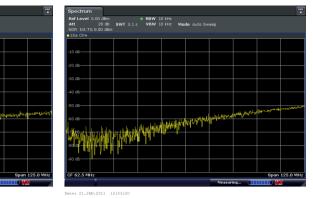

# CAT 5 for Analogue Signal Transmission

#### CATx cable for analogue signal transmission

- Signal transmission over CAT5/6 cable

- Test signal up to 125 MHz sine wave

- Attenuation 0.4 dB / m

Cracow

- Tested with cable lengths up to 10 m

- 4 pixel signals per CAT5/6 cable

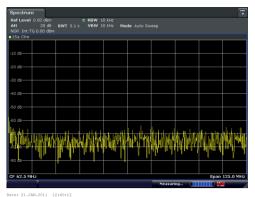

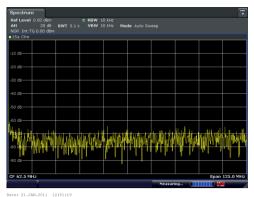

#### CATx cable and connector crosstalk

- CAT5 connectors tested

- Worst crosstalk between channel 2 and 3

- Introduced mainly by the connector

- CAT6 and CAT6a will be tested soon

- Measured crosstalk over whole chain (preamp to FADC): 1% worst case, 0.5% typical

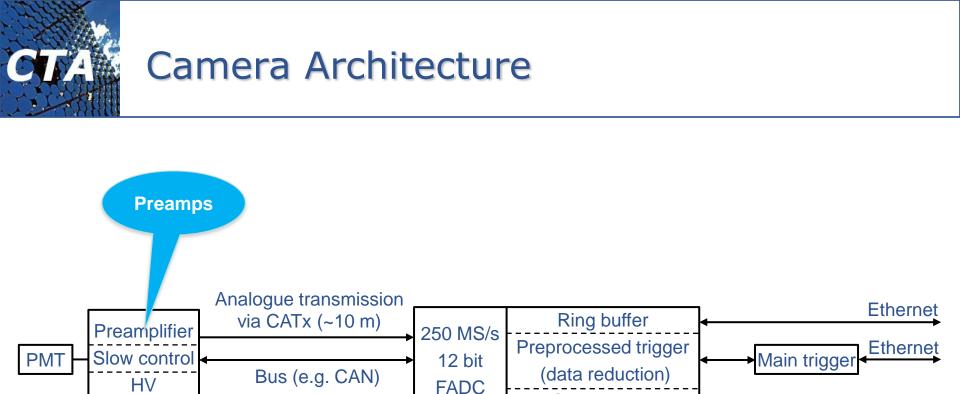

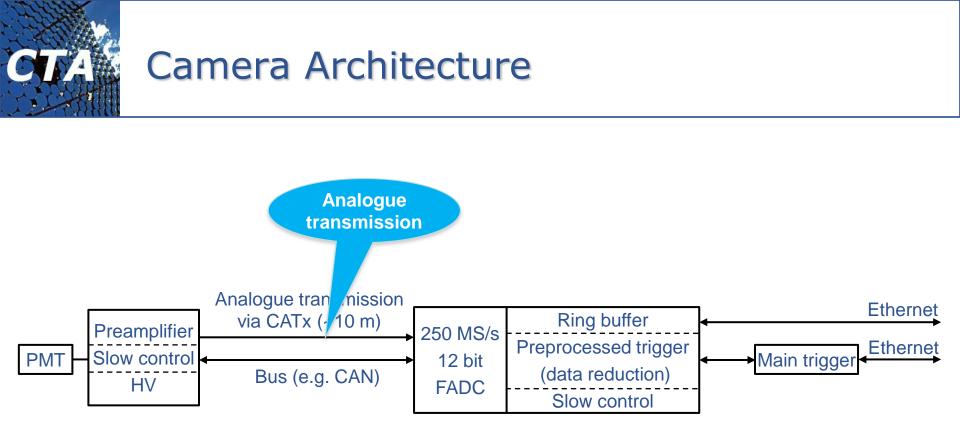

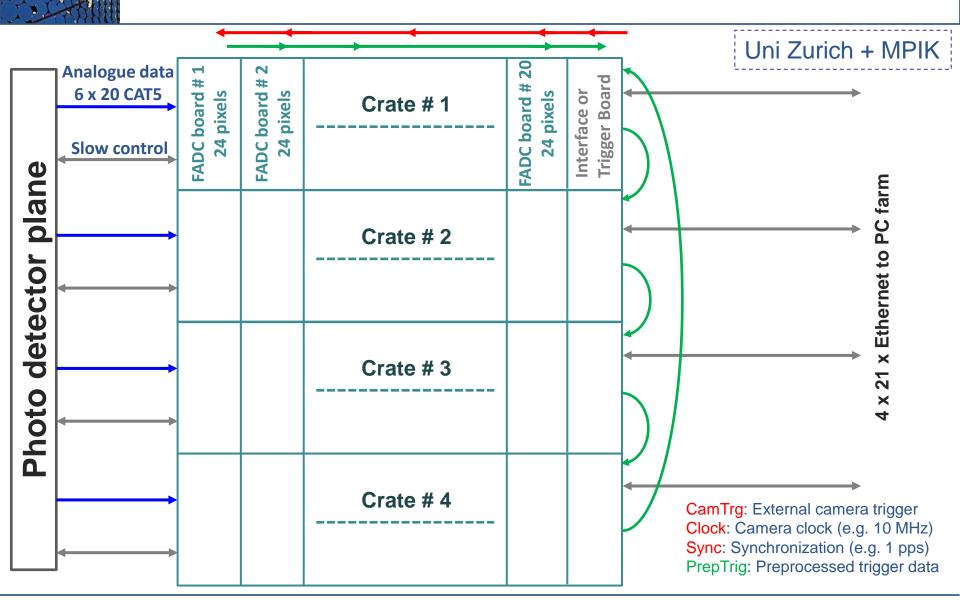

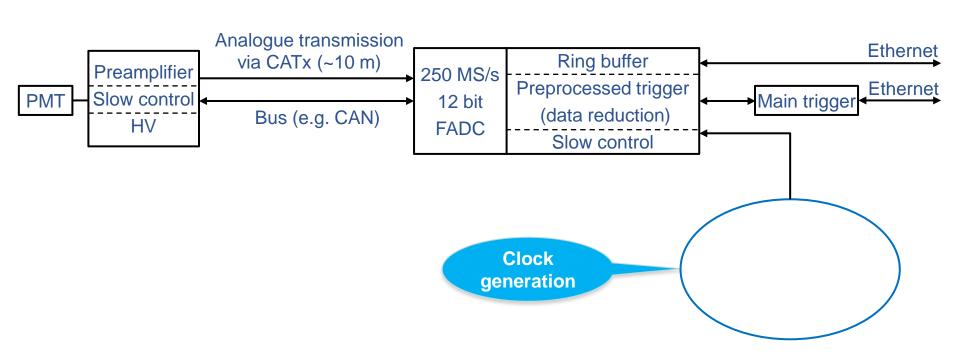

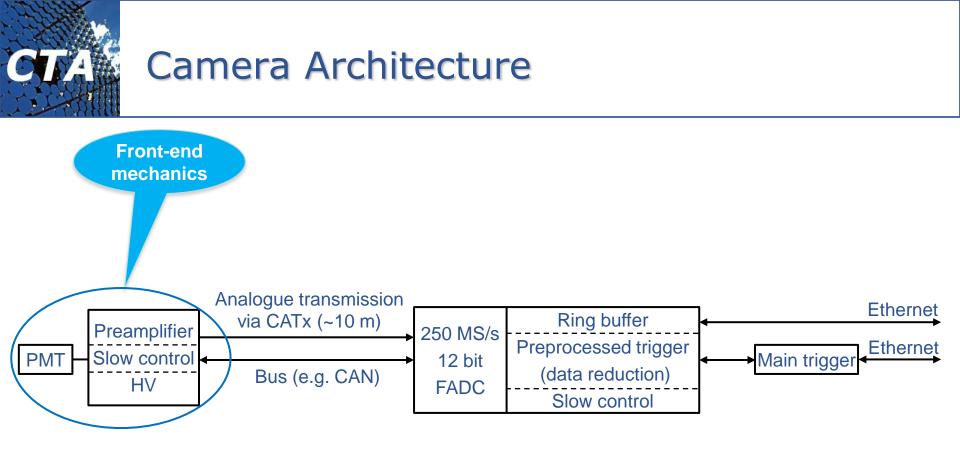

### Camera Architecture

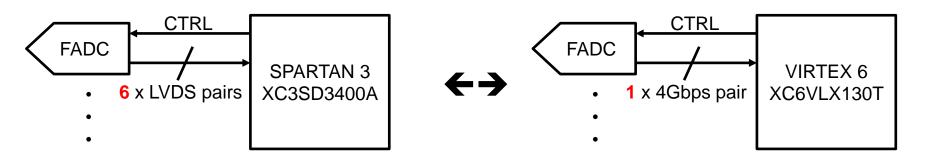

### Parallel vs. Serial FADC to FPGA Data Transmission

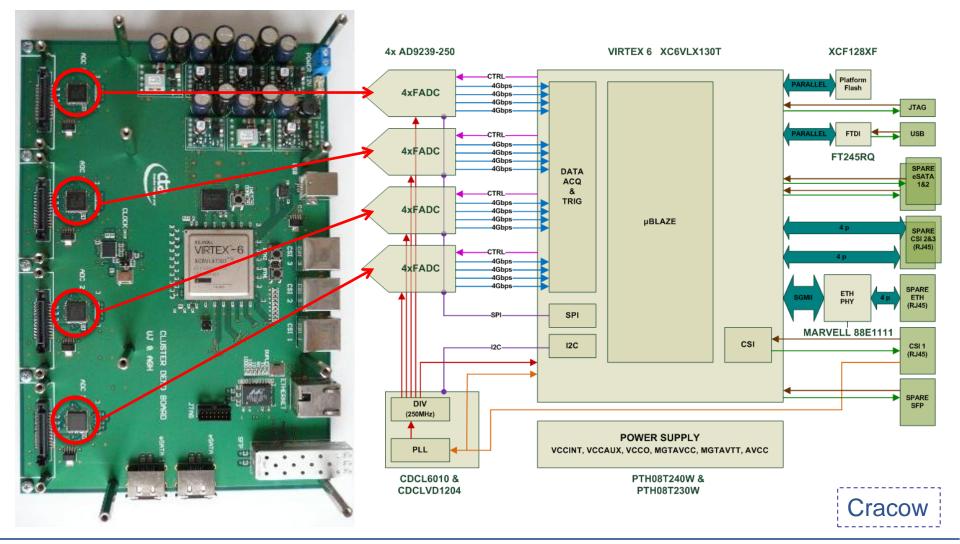

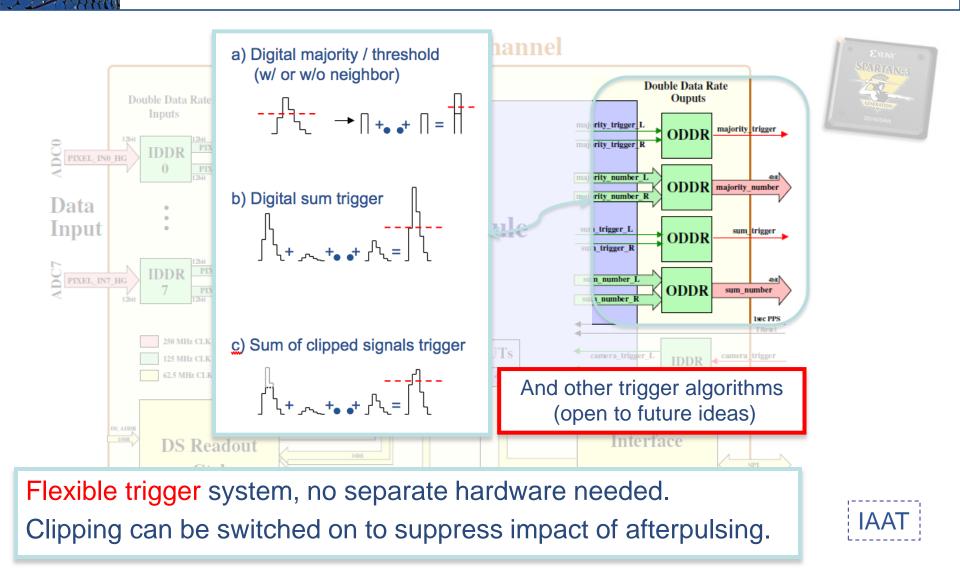

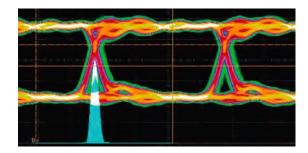

### **Serial FADC interface**

Pin-economical interface to FADC

Expensive FPGA

Cracow

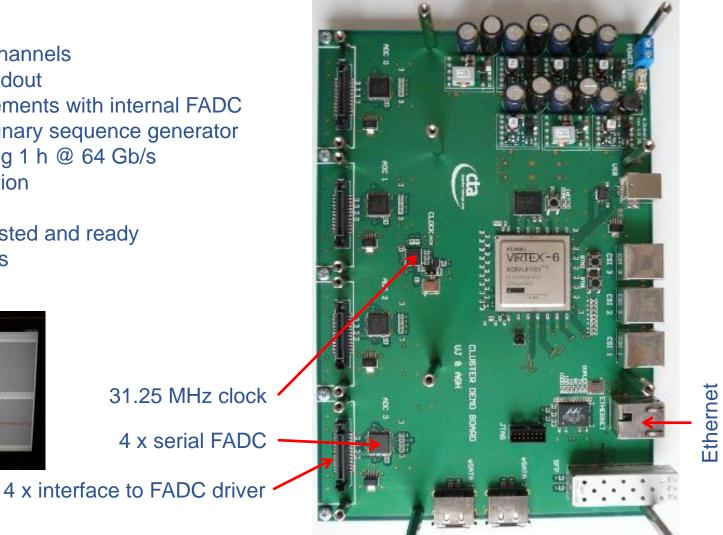

### Serial FADC Demo Board

- 16 serial FADC channels •

- 1Gb Ethernet readout

- Bit error measurements with internal FADC pseudorandom binary sequence generator  $\Rightarrow$  no errors during 1 h @ 64 Gb/s

- **JAVA PC application**

- All sub-circuits tested and ready for measurements

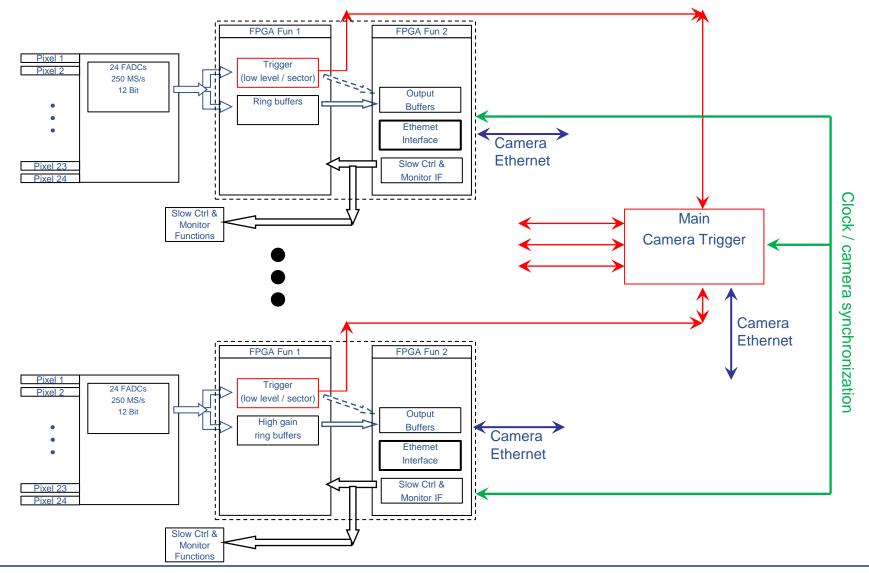

### **Camera Architecture**

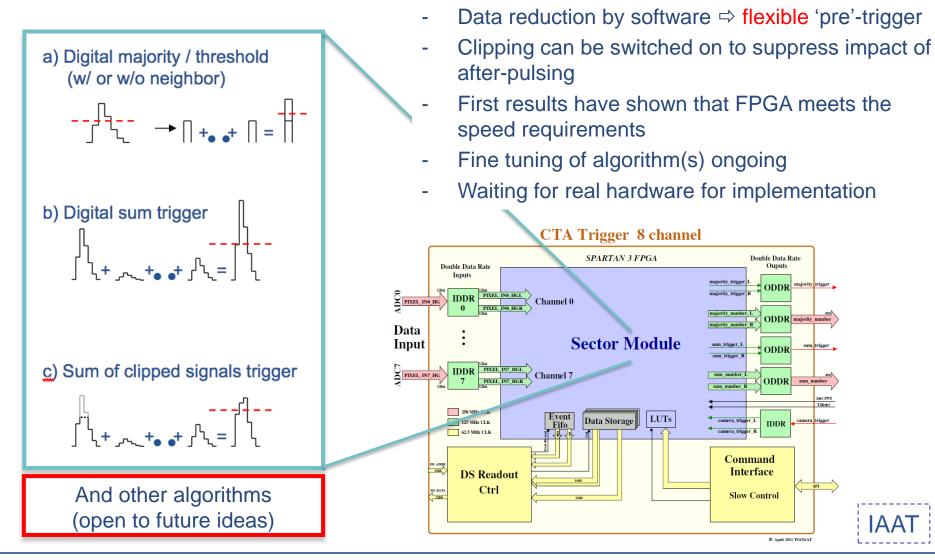

## Preprocessed Trigger FPGA Layout

FlashCam – A fully digital camera for Cherenkov telescopes

2011

### Camera Architecture

CLA

### **Trigger Distribution**

### **Camera Architecture**

CTA

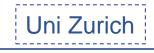

### Trigger Pattern Optimization: Simulations

#### From low-level trigger patterns ...

#### ... to higher-level pattern recognition

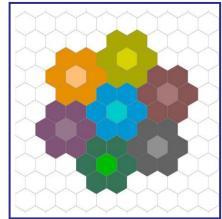

#### E.g.: 7 pixel patch trigger:

- Individual patch sum

- Sum of adjacent pairs

- Sum of adjacent triplets

- Other trigger topologies

⇒ highly flexible and programmable trigger

### Flexible Programmable Trigger

FlashCam – A fully digital camera for Cherenkov telescopes

### CTA Camera Architecture

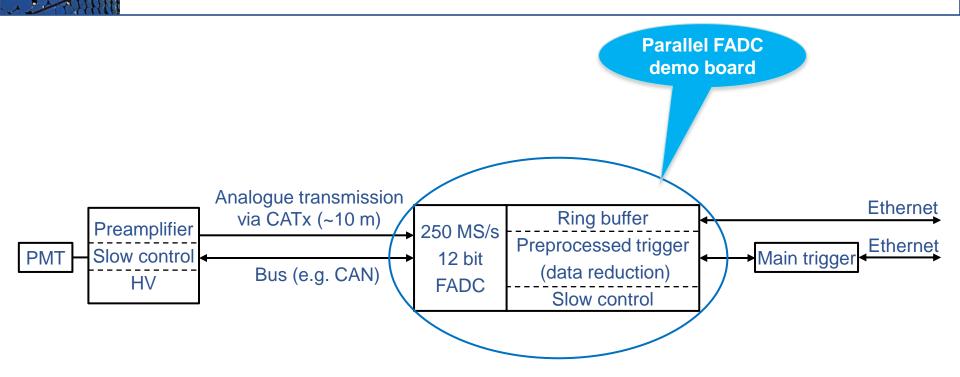

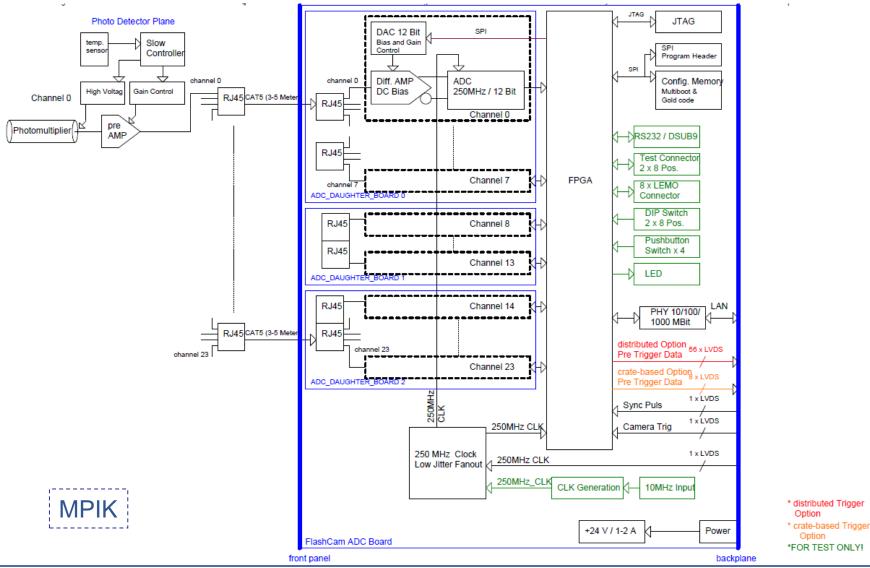

### Parallel FADC Demo Board

- **1** PMT pulse generator

- 2 Preamplifier board

**CI**A

- 3 Analogue signal transmission (CAT5)

- 4 ADC driver board

- 5 Analogue pulse before ADC

- 6 Demo board with 8 parallel FADCs and FPGA

- 7 Event transmission via LAN

- 8 Digitized pulse (4 ns / step)

### Parallel FADC Demo Board

### Measurements and performance see talk: FlashCam performance

CIA

# Camera Architecture

CLA

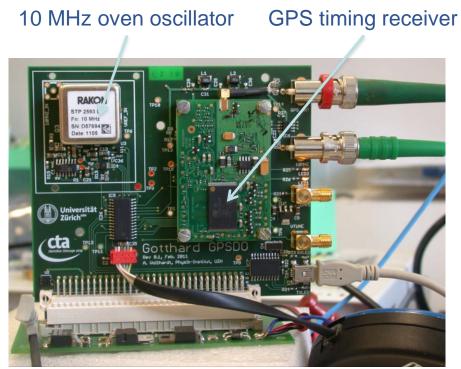

### **Clock Distribution**

Clock generation:

- Single 10 MHz clock generation per telescope

⇒ eliminate need for array-wide clock distribution network

- Steered oscillator (PLL) using GPS 1pps signal compensating for oscillator aging and temperature effects

- Max. phase deviation to UTC ±15 ns

- Max. frequency deviation 1E-10

- Cost effective: < 500 € per unit</li>

Testing in progress. More results in Toulouse.

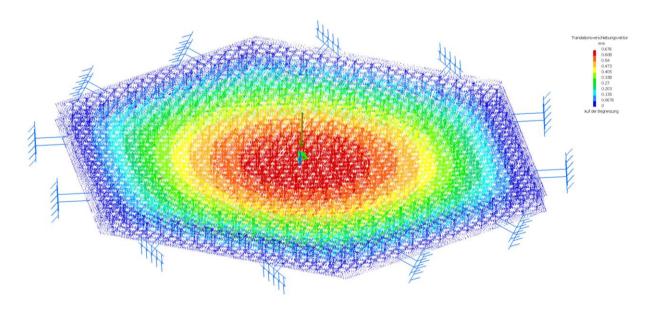

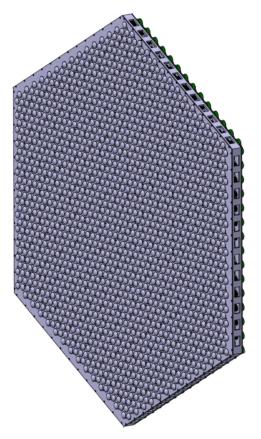

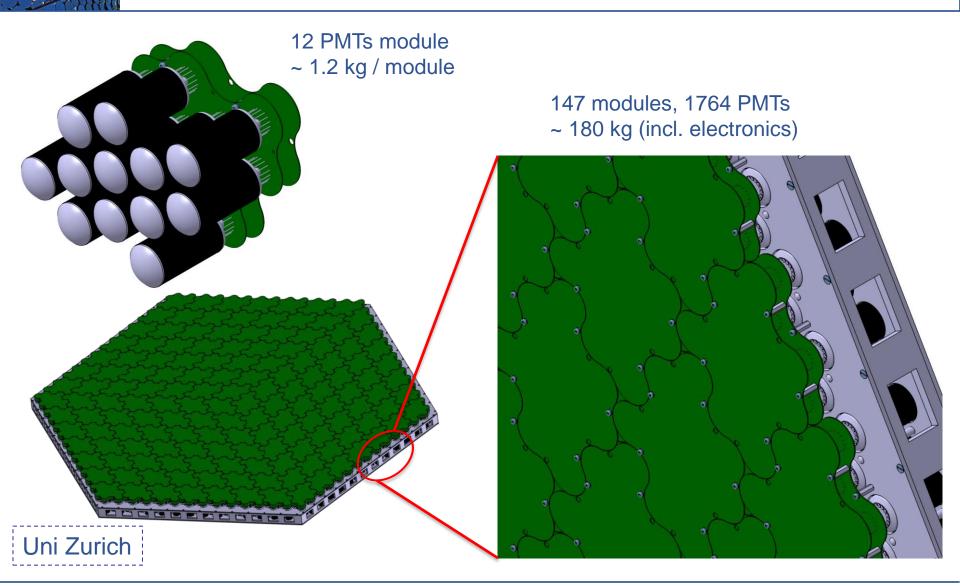

### Front-end mechanics

Structure weight: 81 kg Flat to flat: 2170 mm FEM calculation: 180 kg load at  $90^{\circ} \rightarrow 0.68$  mm sagging

#### Front view (without cones)

### Uni Zurich

### Front-end mechanics

CTA

### Summary and Outlook

#### Outlook

- 24 parallel FADCs demo board planned

- Extensive measurements with serial FADCs demo board

- Test and implementation of main trigger algorithms

- Further development and implementation of slow control concept

- Full camera electronics implementation (PDP module, crates etc.)

### Backup

### FADC-based front-end: Old topology

#### FADC / FPGA based trigger and readout

FlashCam – A fully digital camera for Cherenkov telescopes

CLA

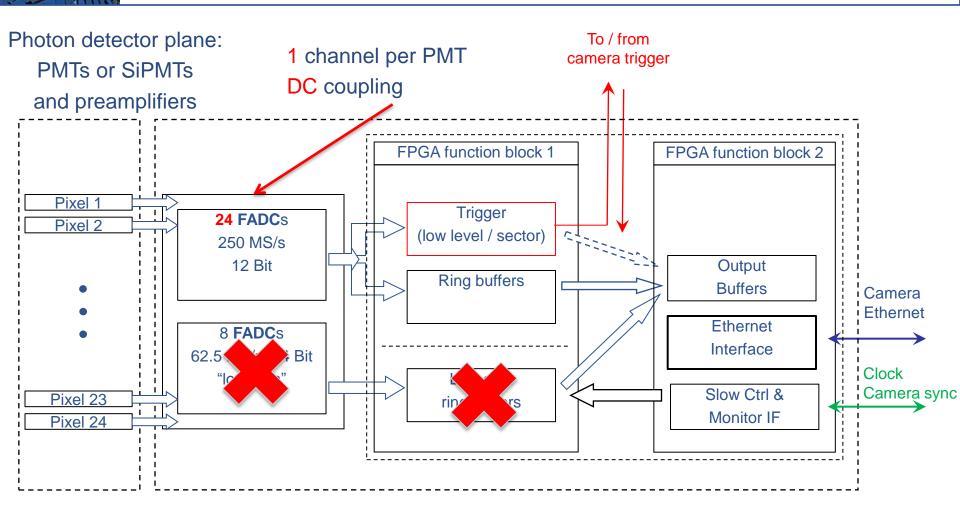

### FADC-based front-end: New topology

#### FADC / FPGA based trigger and readout

FlashCam – A fully digital camera for Cherenkov telescopes

# So the overall Camera Architecture looks like

### FlashCam blockdiagram

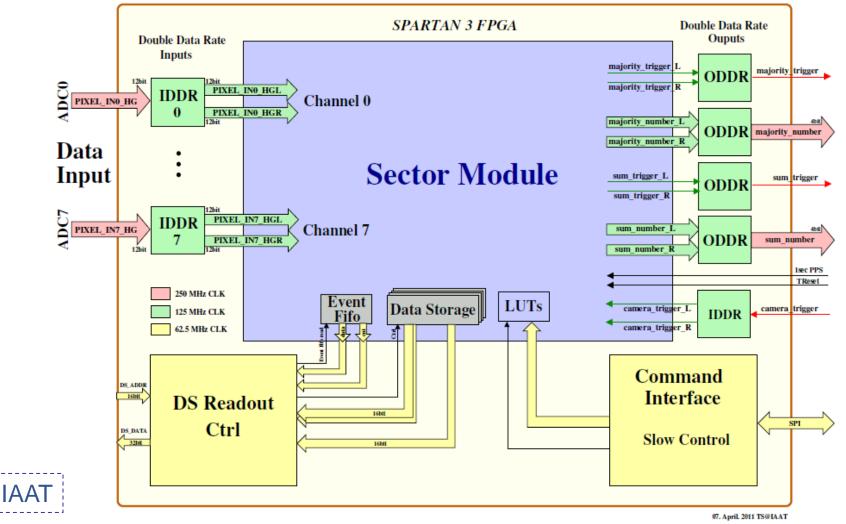

### Sector trigger blockdiagram

#### **CTA Trigger 8 channel**

FlashCam – A fully digital camera for Cherenkov telescopes

N 4 1

5

4

3

2

0

-1

-2

-3

OUTPUT VOLTAGE (V)

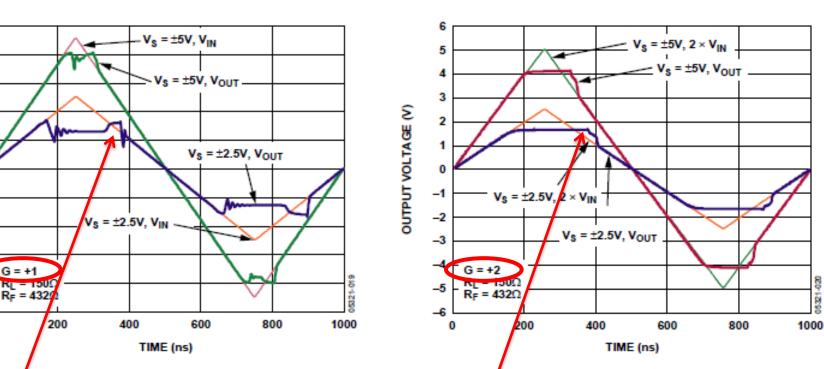

### Saturation preamplifier

Overdrive (AD8000 documentation)

MPIK + Uni Zurich

Overdrive caused by too large input signal

Figure 39. Output Overdrive

Overdrive caused by amplification

Ringing can be avoided with clipping diodes.

G = +1

Saturation of output signal with defined recovery time.

FlashCam – A fully digital camera for Cherenkov telescopes

Figure 38. Input Overdrive

# СТА

### Serial FADC FlashCam Demo Board

### **Ethernet-Based Readout**

|                                                 |                              |                                              |                         |                      | Dead time free                    |  |                                        |                            |               |                |

|-------------------------------------------------|------------------------------|----------------------------------------------|-------------------------|----------------------|-----------------------------------|--|----------------------------------------|----------------------------|---------------|----------------|

| Design parameters:<br>- readout window: 30 nsec |                              |                                              |                         |                      | Sampling<br>Frequency             |  |                                        | Samples Data<br>/event/pix |               | Data Rate      |

| - Assume 1.5 Byte / pix / sample                |                              |                                              |                         |                      | . ,                               |  |                                        | /6                         |               |                |

| - 2000 pixels                                   |                              |                                              |                         |                      | 250 MS/s                          |  |                                        |                            | 10            | ~400 MByte / s |

| - ≤10 kHz camera triggers                       |                              |                                              |                         | 1 GS/s (hi, lo)      |                                   |  |                                        | 60                         | 1.8 GByte / s |                |

|                                                 |                              |                                              |                         |                      | 2 GS/s (hi, lo)                   |  |                                        |                            | 120           | 3.6 GByte / s  |

| Ē                                               | FPGA as<br>Eth sender        |                                              |                         |                      | Tested: 700 MByte/sec (loss free) |  |                                        |                            |               |                |

|                                                 | Pixel 1<br>•<br>•<br>Pixel 8 | Analogue<br>pipeline<br>w/ ADC<br>or<br>FADC | <b>↓</b><br>Buffer/FPGA |                      | RJ 45                             |  | 3 x 48 Port<br>GB Etherne<br>Switch    |                            |               |                |

|                                                 |                              |                                              |                         | 8 x 1 GB<br>Ethernet |                                   |  |                                        |                            |               |                |

|                                                 | Pixel 1                      | Analogue<br>pipeline<br>w/ ADC<br>or<br>FADC | Buffer/FPGA             |                      |                                   |  | ♥<br>PC Server<br>8 x 1 GB<br>Ethernet |                            |               |                |

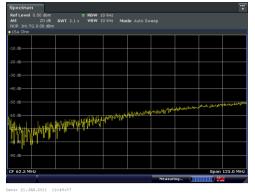

# CAT 5 for Analogue Signal Transmission

No plug inserted

#### CH1 to CH3

#### CH1 to CH4

CF 62.5 MHz

Date: 21.JAN.2011 12:42:00

CH2 to CH3 !!!

Ref Level

0.00 dBm

© RBW 10 kHz

Att

20 dB

SWT 3.1 s

VBW 10 kHz

Mode Auto Sweep

NOR

Int.TG 0.00 dBm

SWT 3.1 s

VBW 10 kHz

Mode Auto Sweep

CH1 to CH2

Date: 21.JAN.2011 12:42:55

Span 125.0 MH

CH2 to CH4

Ref Level

0.00 dBm

© RBW 10 kHz

Att

20 dB

SWT 3.1 s

VBW 10 kHz

Mode

Auto Sweep

NOR

Int.TG 0.00 dBm

0

NOR

Int.TG 0.00 dBm

NOR

Int.TG 0.00 dBm

NOR

NOR

Int.TG 0.00 dBm

NOR

NOR</t

where the word have a relationer

المستحملة فجرأ بسأحط ومغاطين ووريه

#### CH3 to CH4

FlashCam – A fully digital camera for Cherenkov telescopes

2011

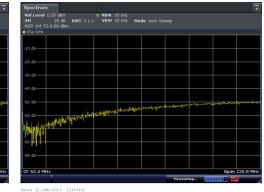

# CAT 5 for Analogue Signal Transmission

Naked plug inserted (no cable)

CH1 to CH2

#### CH1 to CH3

Manufal March 1

#### CH1 to CH4

CF 62.5 MH

Date: 21.JAN.2011 12:54:17

CH2 to CH3 !!!

Ref Level

0.00 dBm

© RBW 10 kHz

Att

20 dB

SWT 3.1 s

VBW 10 kHz

Mode Auto Sweep

NOR

Int.TG 0.00 dBm

SWT 3.1 s

VBW 10 kHz

Mode Auto Sweep

CH2 to CH4

Date: 21.JAN.2011 12:52:12

Span 125.0 MH

RefLevel

0.00 dBm

© RBW 10 kHz

Att

20 dB

SWT 3.1 s

VBW 10 kHz

Mode Auto Sweep

NOR Int.TG 0.00 dBm

VBW 10 kHz

Mode Auto Sweep

NOR Int.TG 0.00 dBm

NOR Int.

#### CH3 to CH4

### Sector FPGA Layout

# CTA

### Clock and Trigger Distribution: Parallel

CAT cables well suited for digital signal transmission at ~ 250 MS/s